## MLS: Multilevel Scheduling in Large Scale High Performance Computers ENSINE

**SWISS NATIONAL SCIENCE FOUNDATION**

Florina M. Ciorba (Principle Investigator), Ahmed Eleliemy, and Jonas H. Müller Korndörfer Department of Mathematics and Computer Science, University of Basel, Switzerland

{firstname.lastname}@unibas.ch **Duration**: September 1, 2017 – August 31, 2020 hpc.dmi.unibas.ch/HPC/MLS.html

## 1. Research Problem

### **Research Question**

Given massive parallelism, at multiple levels, and of diverse forms and granularities, how can it be exposed, expressed, and exploited such that execution times are reduced, performance targets are achieved, and acceptable efficiency is maintained?

## Methodology

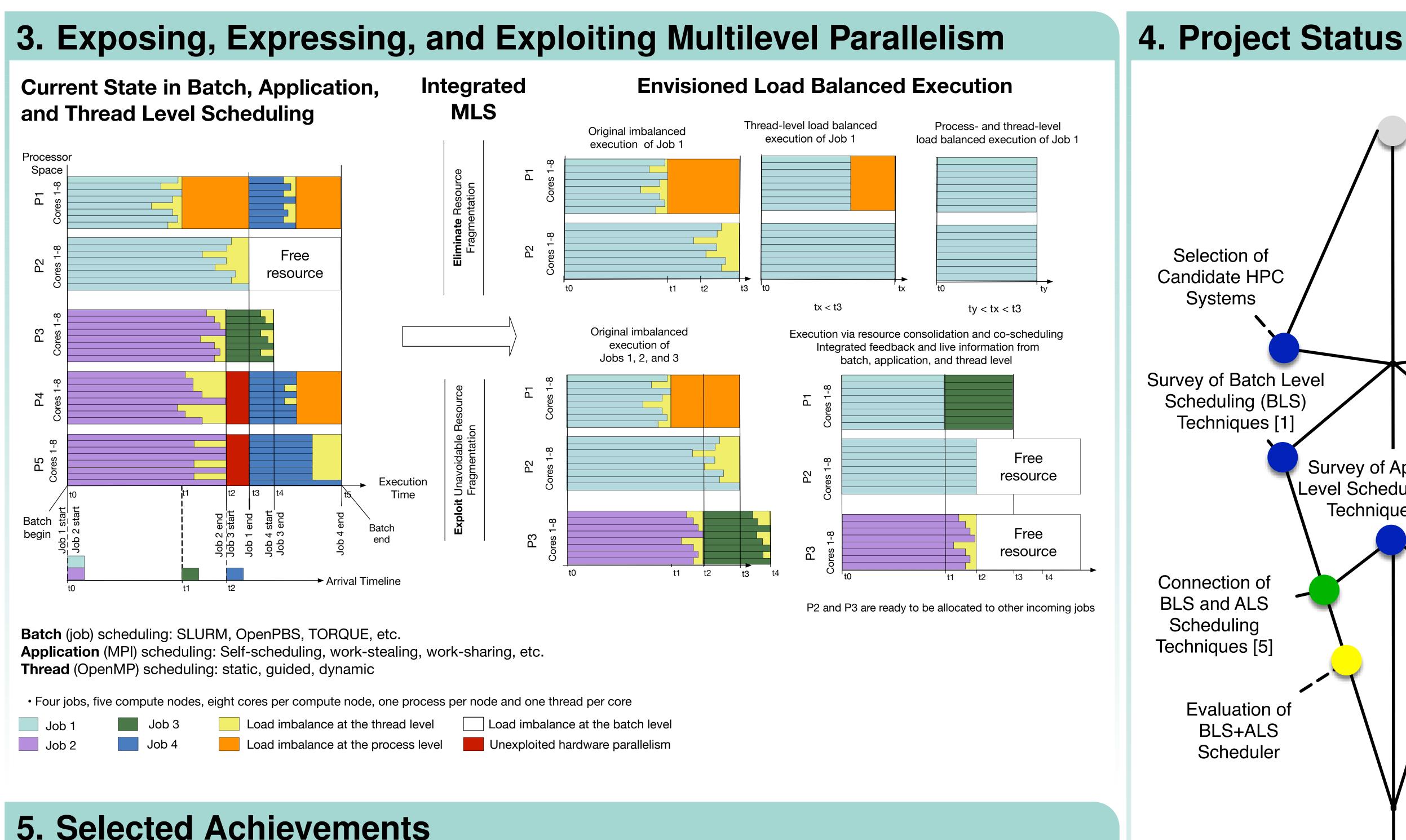

Multilevel scheduling (MLS) extends and bridges the most successful batch (jobs scheduled on a system), application (application processes scheduled on allocated nodes/processors/cores), and thread (application threads scheduled on the allocated cores) scheduling approaches beyond a single or a couple levels of parallelism (scaling across) and beyond their current scale (scaling out).

## **Envisioned Outcomes**

A prototype multilevel scheduling solution that integrates live feedback information from three, currently disjoint, scheduling levels: batch, application, and thread.

## 2. Objectives

Selection of

Candidate HPC

Systems

Survey of Batch Level

Scheduling (BLS)

Techniques [1]

- Leverage all available parallelism within each single hardware parallelism level and across the three hardware parallelism levels (system, node, core).

- 2. Address hardware heterogeneity.

- 3. Achieve robustness against perturbations (including variations and failures) while minimizing execution time, maintaining acceptable efficiency, and maximizing resource utilization.

Survey of Application

Level Scheduling (ALS)

Techniques [2,3]

Project start

Selection of

Candidate HPC

**Applications**

Survey of Thread Level

Scheduling (TLS)

Techniques

Connection of

ALS and TLS

Scheduling

Techniques [4]

**Evaluation of**

ALS+TLS

Scheduler

Evaluation of

**BLS+ALS+TLS**

Scheduler

09/2017

# Connection of **BLS** and ALS Scheduling Techniques [5] **Evaluation of** BLS+ALS Scheduler Connection of BLS, ALS, and TLS Scheduling **Techniques**

Project end \_

09/2020

**LEGEND**

Project start

Next steps

Project end

Completed tasks

Tasks in progress

### Suspend simulation Simulation BLS communication suspend/resume Job execution update manager Job execution Starting Starting Job execution parameters lob simulation Job simulation report report using given ALS ising given ALS fon allocated communication on allocated resources manager manager SimGrid-SD simulation process SimGrid-SD simulation process **ALS simulator instance N ALS simulator instance 1** Legend Internal GridSim events External messages of the connection layer Internal synchronization events of the connection layer Connection layer entities

**Achievement 1**: A two-level simulator for

batch and application level scheduling [1]

GridSim-Alea simulation process

GridSim entity

GridSim simulation engine (1)

registration submission

Scheduler entity

**BLS** simulator instance

GridSim entity Job execution

GridSim entity

Job loader entity

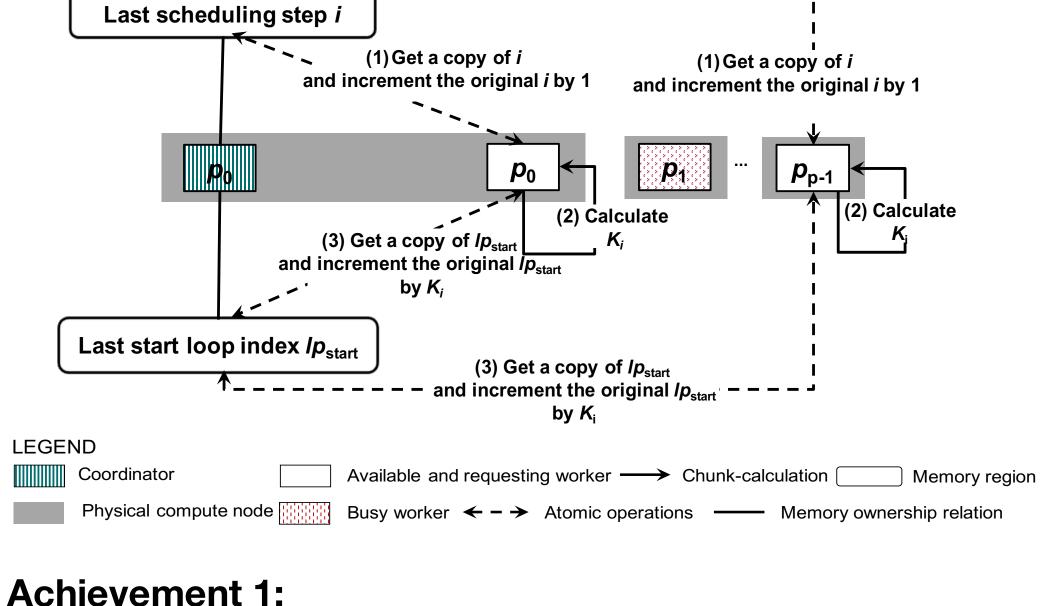

**Achievement 2:** A distributed chunk-calculation approach for dynamic loop scheduling at application level scheduling on heterogeneous distributed-memory systems [5,7]

Introduced a generic simulation approach that bridges two existing simulators from batch and application scheduling levels to explore the relationship between batch and application level scheduling.

## **Achievement 2:**

Introduced a distributed chunk-calculation approach that is recommended for developing DLS techniques on heterogeneous distributed-memory systems for application level scheduling.

## 6. Project Publications

Simulation clock within a simulation instance

- [1] Eleliemy, A. and Ciorba, F. M. "Hierarchical Dynamic Loop Scheduling on Distributed-Memory Systems Using an MPI+MPI Approach", In Proceedings of the 20th IEEE International Workshop on Parallel and Distributed Scientific and Engineering Computing (PDSEC), 2019.

- [2] Eleliemy, A. and Ciorba, F. M. "Dynamic Loop Scheduling Using MPI Passive-Target Remote Memory Access", In Proceedings of the 27th Euromicro International Conference on Parallel, Distributed, and Network-Based Processing (PDP), 2019.

- Mohammed, A., Ciorba, F. M., Cavelan, A., Cabezon, R., and Banicescu, I. "Identifying Performance Challenges in Smoothed Particle Hydrodynamics Simulations", Poster at the Platform for Advanced Scientific Computing Conference (PASC), 2019.

- Eleliemy, A. and Ciorba, F. M. "Dynamic Loop Scheduling Using the MPI Passive-Target Remote Memory Access Model", Poster at the Platform for Advanced Scientific Computing Conference (PASC), 2018. Mohammed, A., Eleliemy, A., Ciorba, F. M., Kasielke, F., and Banicescu, I. "Experimental Verification and Analysis of Dynamic Loop Scheduling in Scientific Applications", In Proceedings of the 17th International Symposium on Parallel and Distributed Computing (ISPDC), 2018.

- Mohammed, A. and Ciorba, F. M. "Sil: An Approach for Adjusting Applications to Heterogeneous Systems Under Perturbations", In Proceedings of the International Workshop on Algorithms, Models and Tools for Parallel Computing on Heterogeneous Platforms (HeteroPar) of the 24th International European Conference on Parallel and Distributed Computing (Euro-Par), 2018.

- [7] Eleliemy, A., Mohammed, A., and Ciorba, F. M. "Exploring the Relation Between Two Levels of Scheduling Using a Novel Simulation Approach", In Proceedings of the 16th International Symposium on Parallel and Distributed Computing (ISPDC), 2017. Eleliemy, A., Mohammed, A., and Ciorba, F. M. "Efficient Generation of Parallel Spin-images Using Dynamic Loop Scheduling", In Proceedings of the 8th International Workshop on Multicore and Multithreaded Architectures and Algorithms (M2A2) of the 19th IEEE International Conference for High Performance

- Computing and Communications (HPCC), 2017. [9] Mohammed, A., Eleliemy, A., and Ciorba, F. M. "A Methodology for Bridging the Native and Simulated Executions of Parallel Applications", Poster at the International Conference for High Performance Computing, Networking, Storage and Analysis (SC), 2017.